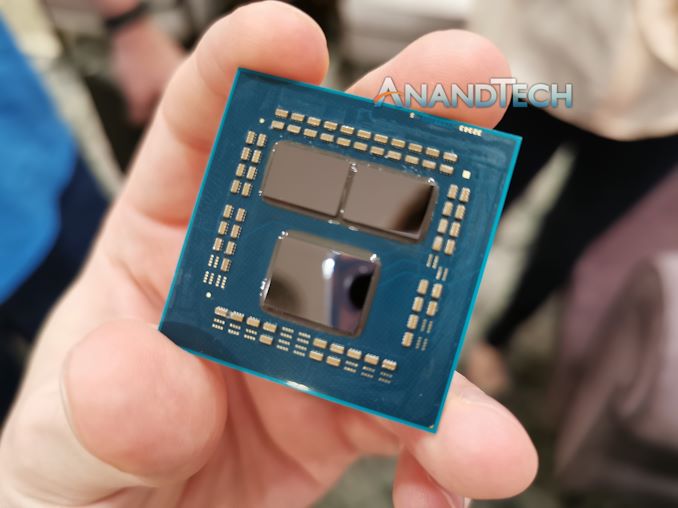

While not the absolute first company in the market to talk about putting different types of silicon inside the same package, AMD’s launch of Ryzen 3000 back in July 2019 was a first in bringing high performance x86 computing through the medium of chiplets. The chiplet paradigm has worked out very well for the company, having high performance cores on optimized TSMC 7nm silicon, while farming the more analog operations to cheaper GlobalFoundries 14nm silicon, and building a high speed interconnect between them. Compared to a monolithic design, AMD ends up using the better process for each feature, smaller chips that afford better yields and binning, and the major cost adder becomes the packaging. But how low cost can these chiplet designs go? I put this question to AMD’s CEO Dr. Lisa Su.

In AMD’s consumer-focused product stack, the only products it ships with chiplets are the high-performance Ryzen 3000 and Ryzen 5000 series processors. These range in price from $199 for the six-core Ryzen 5 3600, up to $799 for the 16-core Ryzen 9 5950X.

Everything else consumer focused is a single piece of silicon, not chiplets. Everything in AMD’s mobile portfolio relies on single pieces of silicon, and they are also migrated into desktop form factors in AMD’s desktop APU strategy. We’re seeing a clear delineation between where chiplets make financial sense, and where they do not. From AMD’s latest generation of processors, the Ryzen 5 5600X is still a $299 cost at retailers.

One of the issues here is that a chiplet design requires additional packaging steps. The silicon from which these processors are made have to sit in a PCB or substrate, and depending on what you want to do with the substrate can influence its cost. Chiplet designs require high speed connections between chiplets, as well as power and communications to the rest of the system. The act of putting the chiplets on a singular substrate also has an effective cost, requiring accuracy - even if 99% accurate placement per chiplet on a substrate means a 3 chiplet product as a 3% yield loss from packaging, raising costs. Beyond this, AMD has to ship its 14nm dies for its products from New York to Asia first, to package them with the TSMC compute dies, before shipping the final product around the world. That might be reduced in future, as AMD is set to make its next-generation chiplet designs all within Asia.

Ultimately there has to be a tipping point where simply building a monolithic silicon product becomes better for total cost than trying to ship chiplets around and spend lots of money on new packaging techniques. I asked the question to Dr. Lisa Su, acknowledging that AMD doesn’t sell its latest generation below $300, as to whether $300 is the realistic tipping point from the chiplet to the non-chiplet market.

Dr. Su explained how in their product design stages, AMD’s architects look at every possible way of putting chips together. She explained that this means monolithic, chiplet, packaging, process technologies, as the number of potential variables in all of this have direct knock-on effects for supply chain and cost and availability, as well as the end performance of the product. Dr. Su stated quote succinctly that AMD looks for what is best for performance, power, cost – and what you say on the tipping point may be true. That being said, Dr. Su was keen not to directly say this is the norm, detailing that she would expect in the future that the dynamic might change as silicon costs rise, as this changes that optimization point. But it was clear in our discussions that AMD is always looking at the variables, with Dr. Su ending on a happy note that at the right time, you’ll see chiplets at the lower end of the market.

Personally, I think it’s quite telling that the market is very malleable to chiplets right now in the $300+ ecosystem. TSMC D0 yields of N7 (and N5) are reportedly some of the industry best, which means that AMD’s mobile processors in the ~200 sq mm range can roll off the production line and cater for everything up to that $300 value (and perhaps some beyond). Going bigger brings in die size yield constraints, where chiplets make sense. We’re now in at a stage where if Moore’s Law continues, how much compute can we fit in that 200 sq mm sized silicon, and which markets can benefit from it – or are we going to get to a point where so many more features are added that silicon sizes would increase, necessarily pushing everything down the chiplet route. As part of the discussion, Dr. Su mentioned economies of scale when it comes to packaging, so it will be interesting to see how this dynamic shakes out. But for now it seems, AMD’s way to address the sub-$300 market is going to be with either last generation hardware, or monolithic silicon.

0 Comments